Karnaugh Map (K-Map) Solved Examples | 2, 3, 4 Variable K-Map

The article explains the Karnaugh Map (K-Map), a graphical method for simplifying Boolean expressions in digital logic design. It discusses the K-Map’s structure, its application for 2-, 3-, and 4-variable problems, techniques for grouping adjacent cells, and utilizing “don’t care” entries for further simplification of logic functions.

January 18, 2012 ECE 152A - Digital Design Principles 30 Combinational Design Example 1 Design Specification Design a logic network that takes as its input a 4-bit, one’s complement number and generates a 1 if that number is odd (0 is not odd) Label the inputs A, B, C and D, where A is the most significant bit

Make states have adjacent assignments (differing by only one bit) if: They have the same next (child) state in the state diagram for the same input They have the same previous (parent) state in the state diagram They have the same output for the same input.

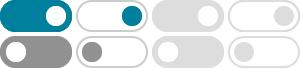

2 variable K-Maps (Adjacency) In an n-variable k-map, each square is adjacent to exactly n other squares Q: What if you have 1 in all squares? The boolean function does not depend on the variable , so it is a fixed logic 1 11

Truth Table Method: This is a simple methodology of the design of digital circuits: The relationship between the inputs and outputs of the circuit is determined by completing the Truth Table.

Logical adjacency is the basis for all Boolean simplification methods. The K–Map approach is a manual procedure that transforms logical adjacency into physical adjacency on the paper.

HW4 - Digital Logic Design - Question1: a) Adjacency Matrix

In The Adjacency list we have 18 blocks and each block. Each block have one. 1) Initialize all vertices as unvisited and unmarked. 2) Perform DFS on G, visiting the vertices in alphabetical order. 3) Mark each vertex with its finishing time. 1) Initialize all vertices as unvisited and unmarked. decreasing order of their finishing times.

June 29, 2009 ECE 152A -Digital Design Principles 30 Combinational Design Example 1 Design Specification Design a logic network that takes as its input a 4-bit, one’s complement number and generates a 1 if that number is odd (0 is not odd) Label the inputs A, B, C and D, where A is the most significant bit Implement your design in standard ...

Karnaugh Maps: Master Simplifying Logic Circuits Effortlessly

Jan 22, 2025 · In the realm of digital electronics, simplifying logic circuits is a crucial skill for designers and engineers. One of the most powerful tools for achieving this is the Karnaugh Map (K-Map). Developed by Maurice Karnaugh in 1953, K-Maps provide a systematic approach to minimizing Boolean expressions, making it easier to design efficient and ...

Example from research 10 Robert Dick Advanced Digital Logic Design. System specification languages ... 27 Robert Dick Advanced Digital Logic Design. System specification languages Brief introduction to VHDL VHDL sequential system design and specification styles Homework

- Some results have been removed